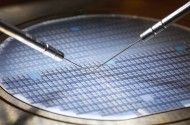

先端半導体パッケージの最新動向と三次元集積化プロセス技術

| 開催日 | 10:30 ~ 16:30 |

|---|---|

| 主催者 | 株式会社 情報機構 |

| キーワード | 半導体技術 電子デバイス・部品 |

| 開催エリア | 全国 |

| 開催場所 | お好きな場所で受講が可能 |

AI需要の増大に伴い、世界的に先端半導体パッケージへの依存度が高まり開発競争も激化!現在の好機を見逃さない様、そのプロセスの基礎・要点を把握し先端技術動向を把握しましょう!

セミナー講師

神奈川工科大学 工学部 電気電子情報工学科 非常勤講師 博士(工学) 江澤 弘和 氏

■ご略歴1985年から(株)東芝にて30年以上先端Si半導体の微細化プロセス及び中間領域プロセスの開発に従事。2017年から東芝メモリ(株)。2018年4月から神奈川工科大学工学部の非常勤講師を兼務。2019年9月に同社(現キオクシア)を定年退職。2020年4月より個人コンサルティング事業(ezCoworks)を開始。現在に至る。

セミナー受講料

1名47,300円(税込(消費税10%)、資料付)*1社2名以上同時申込の場合、1名につき36,300円*学校法人割引;学生、教員のご参加は受講料50%割引。

受講について

- 配布資料はPDF等のデータで送付予定です。受取方法はメールでご案内致します。(開催1週前~前日までには送付致します)※準備の都合上、開催1営業日前の12:00までにお申し込みをお願い致します。(土、日、祝日は営業日としてカウント致しません。)

- 受講にあたってこちらをご確認の上、お申し込みください。

- Zoomを使用したオンラインセミナーです→環境の確認についてこちらからご確認ください

- 申込み時に(見逃し視聴有り)を選択された方は、見逃し視聴が可能です→こちらをご確認ください

セミナー趣旨

あらゆる産業分野におけるAI需要の創出は最先端微細加工による半導体デバイスの高性能化開発に支えられていますが、最近の市場要求の趨勢はチップレベルの性能向上だけでなく、システムレベルの性能向上を先端パッケージ開発に付託する方向を鮮明にしています。 最近の生成AI開発企業や利用企業のGPU争奪戦は、2.5Dパッケージ生産能力の不足やGPUとパッケージ上で機能を繋ぐHBMの供給不足に起因する需給乖離である、とメディアでは喧伝され、更なるHBMの大容量化に伴うパッケージの大型化はパネルレベルパッケージの高品位化開発を促進するための新規設備投資の動機付けとなっています。 日本では半導体産業を取り巻く地政学的な議論が喧しく、産業基盤強化の深耕不足を憂慮する声も聞こえていますが、現在の好機を見逃す理由はありません。世界的に先端半導体パッケージへの依存度が高まり開発競争も激化している中、そのプロセスの基礎や要点を把握しながら、先端技術の動向を常にアップデートしておく必要があります。 本セミナーでは半導体チップの三次元集積化技術を中心に、これまでの開発推移を整理し、基礎プロセスを再訪しながら、先端パッケージの現状と今後の動向を展望します。

受講対象・レベル

・今さら聞けないプロセスの基礎を再確認したい中堅技術者の方・電子材料、装置メーカーでプロセスの理解に不安を感じている若手技術者の方・先端半導体パッケージの動向に関心のある経営企画、新規事業、営業、マーケティング部門の方 など

習得できる知識

・半導体デバイスとパッケージ、ウエーハとパネルの技術階層を横断する中間領域の視点・チップの三次元積層集積化プロセスの基礎・先端半導体パッケージの開発動向 など

セミナープログラム

1. 最近の半導体デバイスパッケージの動向 (2.5D/3.5DパッケージによるAI向け先端製品事例)2. 後工程の高品位化と中間領域プロセスの進展3. 三次元集積化プロセスの基礎とポイント 3-1.半導体デバイスの性能向上 (a) TSVによるメモリ積層プロセスの再訪 (b) nano-TSVによるBSPDN (c) Wafer level hybrid bonding (HB):最近の接合精度向上 (d) CoW/D2W HB:最近の接合歩留まり向上 (e) 樹脂接合によるHB 3-2.システムレベルの性能向上 (a) Logic-on-DRAM SoC:3D積層の原点 (RDL、Micro-Bumping、Mass reflowによるChip積層の導入) (b) 2.5Dパッケージの開発推移 (c) Si interposer (d) Organic/RDL interposer (e) Si bridge (f) DamasceneプロセスによるRDLの微細化・多層化4. Fan-Out(FO)型パッケージの基礎とポイント 4-1.FOWLPの市場浸透 4-2.プロセス選択肢の拡大:Chip First/RDL first x Face-up/down 4-3.Through Mold Viaプロセス選択肢の拡大による3D FOの民主化 4-4.Panel Level Process/Package (PLP)高品位化の課題5. 市場概況と今後の開発動向 5-1.マスクレス露光によるレティクル制約の解放 5-2.Glass interposer/substrate, Co-packaged Opticsの動向 5-3.メモリパッケージの変化6. Q&A

※上記の講演内容の項目は変更になる可能性があります。