半導体チップは、現代の電子機器の心臓部として、私たちの生活に欠かせない存在となっています。その製造プロセスは、非常に高度で複雑な技術を必要とし、数十年にわたる研究と開発の成果によって進化してきました。半導体の歴史は、1940年代のトランジスタの発明に始まり、集積回路の登場を経て、現在のマイクロプロセッサやメモリチップへと発展しました。この進化の過程では、技術革新が次々と生まれ、チップの小型化や高性能化が実現されてきました。しかし、パターン化の困難性は依然として大きな課題です。微細化が進む中で、製造プロセスにおける精度やコスト、材料の選定など、多くの要因が影響を及ぼします。これらの課題を克服するためには、さらなる技術革新と研究が求められています。今回は、半導体チップの製造プロセスの概要と、その歴史的背景、そしてパターン化における困難性について詳しく探っていきます。

1. 半導体チップにおける製造プロセスとは

半導体チップの製造プロセスについて解説します。半導体チップは、電子機器の心臓部として機能する重要な部品です。その製造プロセスは非常に複雑で、多くのステップから成り立っています。主なプロセス概要は次の通りです。

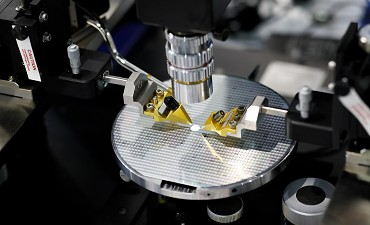

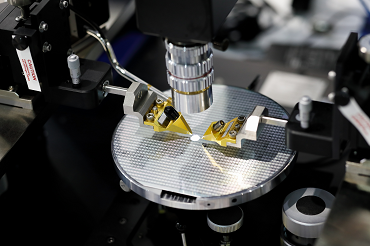

- ウェハーの製造・・・半導体チップはシリコンウェハーと呼ばれる薄い円盤から作られます。まず、シリコンを高純度で結晶化し、円盤状にスライスします。

- 酸化・・・ウェハーの表面に酸化シリコン層を形成します。これは、後の工程での絶縁体として機能します。

- フォトリソグラフィ・・・ウェハーに感光性のレジストを塗布し、紫外線を使ってパターンを転写します。この工程で、チップの回路パターンが形成されます。

- エッチング・・・フォトリソグラフィで作成したパターンに基づいて、不要な部分を化学薬品で削り取ります。これにより、シリコンウェハー上に微細な構造が形成されます。

- ドーピング・・・特定の領域に不純物を添加して、半導体の...