これは2010年の品質工学研究発表大会で、東芝の岡川宏之さんが発表した「半導体製造プロセスにおけるT法活用による超効率的プロセス条件最適化」を要約したものです。

例えば半導体のプロセス実験では、一回の実験に数週間の時間と多大な費用がかかる事から、できるだけ少ない実験で結果を出したいところです。そこでL9などの小さな直交表を使うと少ないパラメータしか扱う事ができず、特性のトレードオフが発生しやすくなるため、L18などの大きめな直交表を使いたいところです。

そこでこの発表者は、T法が項目数よりも小さなサンプル数で解析可能であることに目を付けて、直交表部分実験とT法を活用する事により効率的にパラメータ設計を実施する手法を考案しました。

これによって、L18やL36など大きな直交表に因子を割り付けて、従来と比べて少ない実験回数で主効果解析を行う事ができます。

さらに、部分直交表における水準振りの幅と偏りを考慮してパラメータを割付け、相関行列を用いた因子間の相関係数をチェックすることで主効果の混同を防止しています。

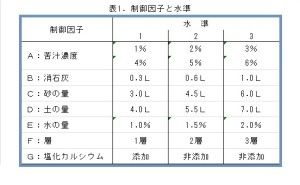

これを半導体メモリ製造の薄膜堆積工程に適用し、L18直交表に8因子を割り付けた組合せの8実験のみで、成膜速度とその面内均一性を共に向上させるようなプロセス条件最適化を実現し、従...